I had an interesting conversation with Jochen this week regarding a bit of code he found on page 98 of the Intel MCS-4 User's Manual. This is a short program intended to test the operation of the MCS-4 Evaluation Kit using the 4009-0009 interface chip. The program begins as shown here:

As a programmer, this makes little sense. The BBL (Branch Back and Load Accumulator) instruction is intended to return from a subroutine call. Yet here it's executed without a previous subroutine call (JMS) instruction being executed. Jochen asked, wouldn't this result in an infinite loop or other erroneous behavior?

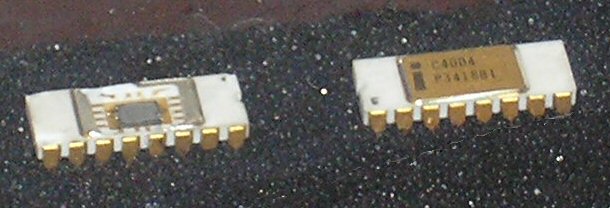

My first reaction was to agree with him. Surely this must be a typographical error? After thinking about it more carefully, I realized the answer to that is no. This code has a deterministic and defined behavior. To understand why, it's necessary to look a bit more closely at the design of the Intel 4004 CPU.