I'd always intended to implement the Instruction Pointer board first. It has an interesting mix of dynamic logic, NAND and NOR gates, and even four flip-flops forming two 2-bit counters. If I end up doing only one board, this is the one I want to do.

That it also has the most components makes it a good test for my area analysis too. If everything allocated to this board fits, the other boards will probably fit too.

I experimented with the layout of the DRAM cells for a while before settling on a 0.160" x 0.160" component placement grid, with each DRAM cell occupying a 2x2 square of the grid (0.320" x 0.320"). This puts the transistors close enough to minimize wasted space, while still allowing room for my tweezers and soldering iron. Or so I hope!

Each 2x2 square is laid out just like in the schematic, with the write enable gate in the lower left, the storage element in the lower right (the 3 pad package), and the read enable gate in the upper right. So what is the 2 pad package in the upper left of the square?

One of the great unknowns in this design is whether the input capacitance of the storage element FET will be high enough to hold the bit state through a full refresh interval. It works on my solderless breadboard, but I don't know whether that's because the breadboard adds parasitic capacitance. Rather than discovering that I need additional capacitance at that point and having to trash the board, I've added a footprint for a discrete capacitor in the fourth grid square. If the circuit has sufficient margins without it I'll leave that space unpopulated, but if needed I'll have a place to put it.

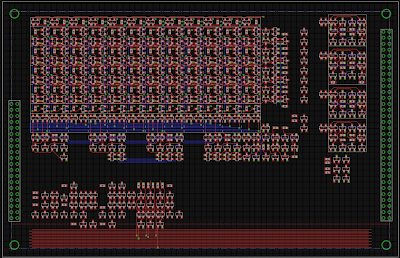

Yesterday I started the layout of this board for real. I got the entire 12x4 array of DRAM cells placed and routed, along with the output precharge FETs across the top and the output inverters along the bottom. I also placed the 3:1 muxes below that and the row decode components along the right edge of the array, but they're not routed.

Here's a snapshot of the board thus far (click to expand):

I've placed all but a handful of the 248 components from Sheet 1, which puts me at about the half-way point with more than half of the board area remaining. There should be enough room to place and route the rest of the components I've assigned to this board, but I'm a bit worried that I'll be forced to place the random logic on a larger grid to get it routed. Worst case, the components on Sheet 4 or 5 could be moved to the timing board, but that would bode poorly for the rest of my area analysis.

My hope is that everything will fit nicely enough that I can go ahead and build this board without doing the layout for the others first, but if things get really tight I might feel the need to finish all the layout first. And that might start feeling like real work.